# Fabrication and Characterization of Polymer-Enhanced TSVs, Inductors, and Antennas for Mixed-Signal Silicon Interposer Platforms

Paragkumar A. Thadesar, *Member, IEEE*, and Muhammed S. Bakir, *Senior Member, IEEE*

**Abstract**—This paper demonstrates the fabrication and high-frequency characterization of polymer-enhanced technologies for a mixed-signal silicon interposer platform. First, the fabrication of 60- $\mu\text{m}$ -diameter and 285- $\mu\text{m}$ -tall photodefined polymer-embedded vias is demonstrated. Their losses are extracted using L-2L and open-short de-embedding techniques up to 30 GHz followed by parasitics extraction. Moreover, eye-diagram measurements are demonstrated for the vias at 10 Gb/s. Second, the fabrication and impedance extraction of 65- $\mu\text{m}$ -diameter and 285- $\mu\text{m}$ -tall photodefined polymer-enhanced coaxial vias are demonstrated. Finally, utilizing the photodefined polymer-enhanced silicon interposer technology, high-performance inductor and antenna are demonstrated over polymer wells.

**Index Terms**—Antennas, coaxial through-silicon vias (TSVs), de-embedding, eye diagrams, inductors, silicon interposer, TSV.

## I. INTRODUCTION

SILICON interposers with dense fine-pitch metallization and through-silicon vias (TSVs) have widely been explored for high-bandwidth density communication between heterogeneous ICs [1]–[3]. Moreover, silicon interposers provide opportunities for the integration of inductors and antennas close to the ICs yielding compact radio-frequency (RF) and analog/mixed-signal systems. The integration of inductors on silicon interposers can improve the performance of circuits, such as digital-controlled oscillators, low-noise amplifiers, and power amplifiers [4]. Moreover, the integration of antennas on silicon interposers can enable a wide range of applications, specifically for those in the millimeter-wave frequency bands (30–300 GHz) with smaller antenna sizes. For example, the frequency band around 60 GHz has been explored for high-speed multimedia transfer and short-range communications [5]; the band around 28 GHz has been explored for future 5G communications [6]; the band around 77 GHz has

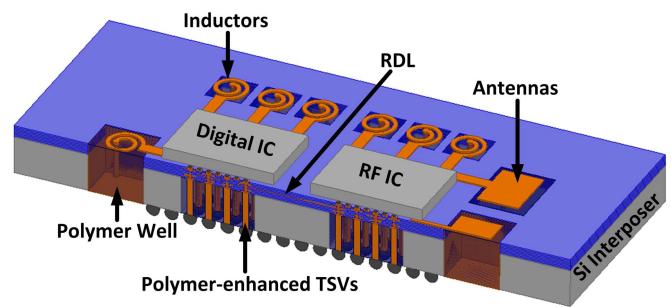

Fig. 1. Envisioned mixed-signal silicon interposer platform featuring polymer-enhanced TSVs, antennas, and inductors.

been explored for radars in automobiles [7]; and the D-band has been explored for medical imaging and picocell cellular links [8].

For the integration of heterogeneous ICs with antennas and inductors close to the ICs, large-area silicon interposers are desired [5], [9]. Greater silicon thickness (larger than 300–400  $\mu\text{m}$ ) is desired as well for large-area interposers to minimize warpage and bow and improve mechanical stability [10], [11]. However, increasing the interposer thickness results in longer TSVs with increased losses [12]. These factors drive the need for low-loss TSV technologies for large-area thick interposers to compensate for the increased length. To reduce the TSV losses, thick polymer [13], air liners [14], and coaxial TSVs [15], [16] have been explored in the literature. In addition to the TSV loss, the presence of silicon near antennas and inductors results in lower radiation efficiency and  $Q$ -factor, respectively [17], [18]. This performance degradation demands innovative antenna and inductor integration technologies within silicon interposers. High-resistivity silicon and glass have been explored in the literature to obtain high-performance passives as well as low-loss TSVs [19], [20].

To address the need for novel low-loss TSVs and high-performance inductors and antennas on silicon interposers, this paper demonstrates the fabrication and characterization of a polymer-enhanced and photodefined silicon interposer platform featuring: 1) polymer-embedded via (PEV)

Manuscript received May 23, 2015; revised September 20, 2015; accepted November 18, 2015. Date of publication January 26, 2016; date of current version March 10, 2016. Recommended for publication by Associate Editor D. G. Kam upon evaluation of reviewers' comments.

The authors are with the School of Electrical and Computer Engineering, Georgia Institute of Technology, Atlanta, GA 30332 USA (e-mail: pthadesar3@gatech.edu; muhannad.bakir@mirc.gatech.edu).

Color versions of one or more of the figures in this paper are available online at <http://ieeexplore.ieee.org>.

Digital Object Identifier 10.1109/TCMT.2015.2511067

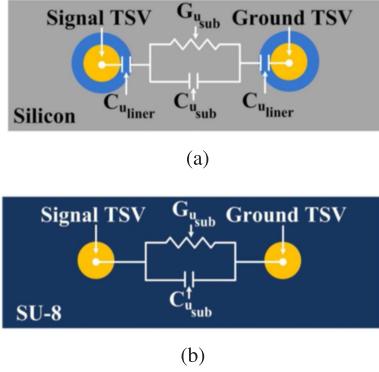

Fig. 2. Top view of parasitic schematic for signal-ground TSV pairs. (a) PEVs. (b) TSVs with  $\text{SiO}_2$  liner.

fabrication, loss de-embedding up to 30 GHz, capacitance and conductance extraction, and eye-diagram measurements; 2) polymer-enhanced coaxial via fabrication and impedance extraction up to 50 GHz; 3) polymer-enhanced inductor fabrication, RF measurements, and  $Q$  and  $L$  extractions; and 4) polymer-enhanced antenna fabrication and  $W$ -band measurements. An envisioned mixed-signal system using the proposed technologies is shown in Fig. 1.

This paper describes the analysis, fabrication, and measurements of PEVs in Section II. The fabrication and characterization of polymer-enhanced coaxial vias are described in Section III. Finally, the fabrication and characterization of polymer-enhanced inductor and antenna are demonstrated in Section IV. Finally, the conclusion is drawn in Section V.

## II. POLYMER-EMBEDDED VIAS

Vias within dielectric regions in silicon have been shown in the literature, including: 1) metal-coated silicon pillars in polymer wells [21] and 2) copper vias in reflowed glass [22]. This paper focuses on utilizing SU-8 [23] photodefinition to fabricate low-loss PEVs.

### A. Analysis

To compare the high-frequency parasitics of PEVs and TSVs with  $\text{SiO}_2$  liner, an electrical analysis is performed for signal-ground TSV pairs. TSV high-frequency electrical modeling has widely been explored in [19] and [24]–[26]. TSVs, in this paper, are modeled using resistors and inductors with conductance and capacitances between the signal and ground TSVs, as shown in Fig. 2. For the TSVs with  $\text{SiO}_2$  liner, the path between the signal and ground TSVs consists of per-unit-length substrate capacitance  $C_{u_{sub}}$ , substrate conductance  $G_{u_{sub}}$ , and dielectric capacitances  $C_{u_{liner}}$ . For PEVs, the path between the signal and ground TSVs consists of only per-unit-length substrate capacitance  $C_{u_{sub}}$  and substrate conductance  $G_{u_{sub}}$ , since a dielectric liner is not present.

The formulas utilized for per-unit-length resistance, inductance, conductance, and capacitance ( $RLGC$ ) evaluation are demonstrated in [19] and [25]. Once the per-unit-length

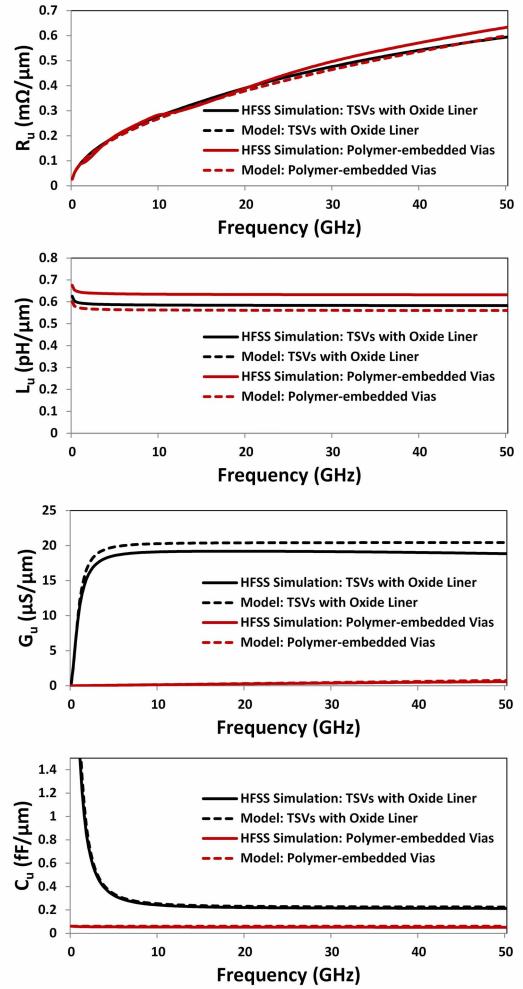

Fig. 3. Evaluated per-unit-length TSV  $RLGC$  values using models and HFSS simulations.

$RLGC$  values are calculated, electromagnetic simulations are performed for comparison using ANSYS high-frequency structure simulator (HFSS), as described in [19]. The per-unit-length  $RLGC$  values for the TSVs with  $\text{SiO}_2$  liner and PEVs are shown in Fig. 3; copper vias are 70  $\mu\text{m}$  in diameter and on a 150- $\mu\text{m}$  pitch. The thickness of the  $\text{SiO}_2$  liner is 1  $\mu\text{m}$ . The relative dielectric constants of silicon and  $\text{SiO}_2$  are 11.68 and 3.9, respectively [27]; silicon resistivity is 10  $\Omega\cdot\text{cm}$ . Moreover, with respect to the properties of SU-8, broadband  $\epsilon_r$  and  $\tan \delta$  characterizations have extensively been shown in the literature using techniques such as microstrip transmission lines, conductor-backed coplanar waveguide transmission lines, microstrip ring resonators, and T resonators [28]–[30]. The broadband  $\epsilon_r$  and  $\tan \delta$  values characterized in the literature up to 210 GHz are close to 3 and 0.04, respectively, and have been used in this paper.

As shown in Fig. 3, PEVs attain 96.2% and 72.8% reduction in conductance and capacitance at 50 GHz, respectively, compared to TSVs with the  $\text{SiO}_2$  liner and the same copper via dimensions. The reduction in the capacitance and conductance of PEVs provides a low-loss electrical performance and hence will be focused upon later in this paper.

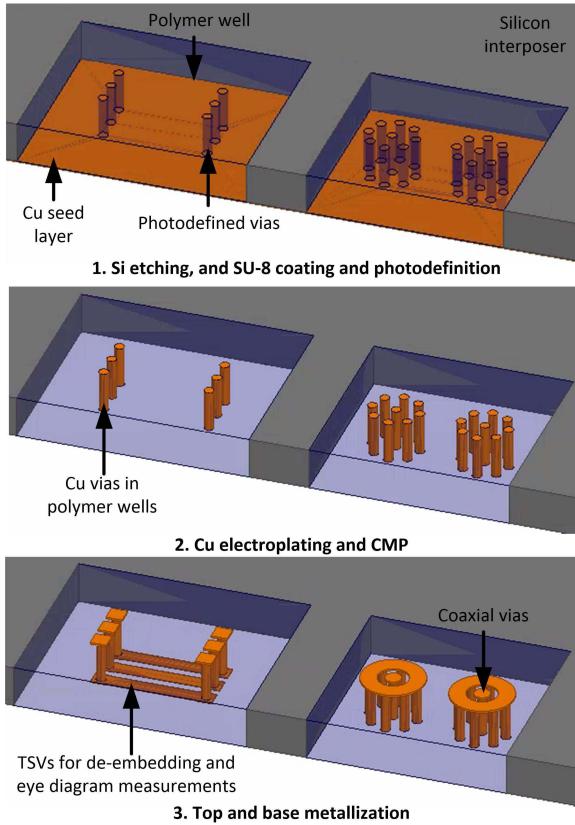

Fig. 4. Fabrication process for polymer-enhanced TSVs.

### B. Fabrication

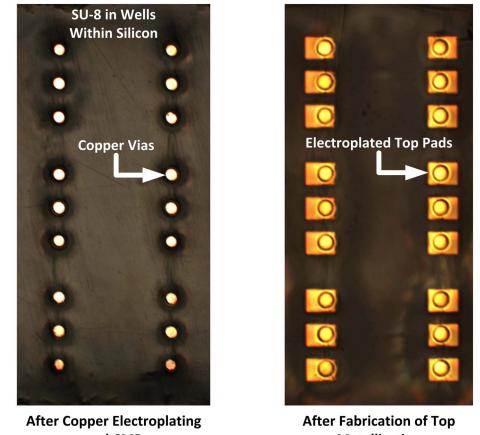

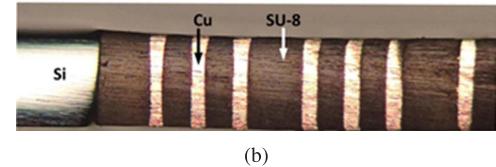

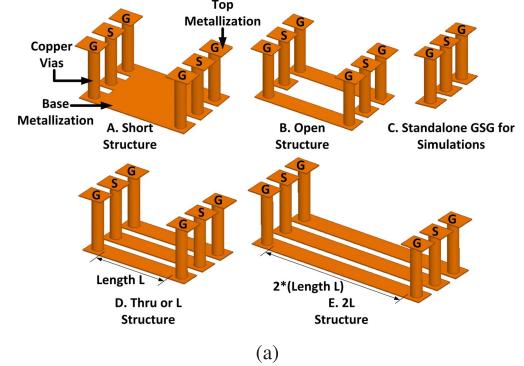

The fabrication process of the polymer-enhanced TSVs under consideration is shown in Fig. 4. The fabrication process begins with the formation of wells (using the Bosch process) in a silicon wafer containing a copper seed layer at the base. Next, SU-8 coating, photodefinition, via electroplating and chemical-mechanical polishing (CMP) are performed to obtain copper vias in the photodefined polymer wells [13]. The vias are fabricated in ground-signal-ground (GSG) and coaxial (described in Section III) configurations. Next, the top and base metallizations are fabricated over the copper vias to attain the following structures: 1) de-embedding and eye-diagram measurement structures with pads over the vias and traces at the base and 2) coaxial via impedance extraction structures, as described in Section III.

### C. RF De-Embedding and CG Extraction

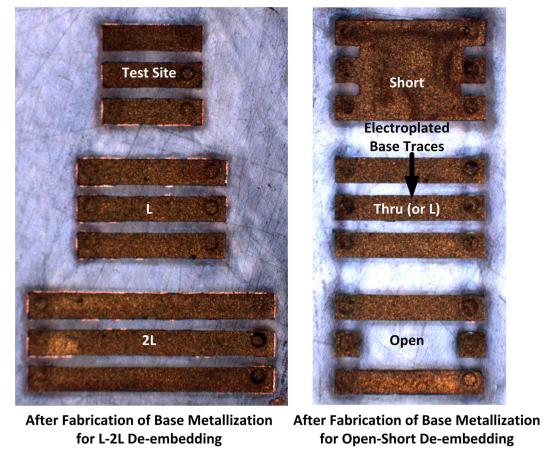

To perform de-embedding of PEVs, two methodologies are implemented: 1) L-2L [31] and 2) open-short [32]. The schematics of the structures fabricated and characterized for de-embedding are shown in Fig. 5(a). A standalone PEV structure is simulated for the sole purpose of benchmarking its results to those obtained from de-embedding. Moreover, a standalone TSV structure with  $\text{SiO}_2$  liner is also simulated (for the comparison of PEVs to the TSVs with 1- $\mu\text{m}$ -thick  $\text{SiO}_2$  liner and  $10\text{-}\Omega\cdot\text{cm}$  silicon resistivity). In the de-embedded TSV structures and the standalone structures for benchmarking, the contribution of the top and bottom pads

Fig. 5. PEVs. (a) Schematics of measured and simulated TSV structures for de-embedding. (b) Cross-sectional view of the fabricated vias. (c) De-embedding and time-domain (L or thru) measurement structures.

is included owing to the de-embedding methodologies used. With further development in de-embedding methodologies, a de-embedding of TSVs without pads can be obtained in the future.

Using the process in Fig. 4, the fabricated PEVs for de-embedding are shown in Fig. 5. The fabricated vias are

285- $\mu\text{m}$  tall, 60  $\mu\text{m}$  in diameter, and on a 150- $\mu\text{m}$  pitch within 1800  $\mu\text{m} \times 1800\text{-}\mu\text{m}$  wells; the traces are 105- $\mu\text{m}$  wide.

For L-2L de-embedding [31], TSV-trace-TSV structures with the 400- and 800- $\mu\text{m}$ -long traces between the TSVs (with pads) were fabricated, simulated, and measured. The measured and simulated  $S$ -parameters of PEVs are converted to  $ABCD$ -parameters, and the TSV losses are extracted as follows:

$$\mathbf{ChainL} = \mathbf{TSV} * \mathbf{Trace} * \mathbf{TSV} \quad (1)$$

and

$$\mathbf{Chain2L} = \mathbf{TSV} * \mathbf{Trace} * \mathbf{Trace} * \mathbf{TSV} \quad (2)$$

where **ChainL**, **Chain2L**, **TSV**, and **Trace** represent the matrices of  $ABCD$ -parameters. Moreover, **ChainL** represents the TSV-trace-TSV structure with the 400- $\mu\text{m}$ -long traces between the TSVs, **Chain2L** represents the TSV-trace-TSV structure with the 800- $\mu\text{m}$ -long traces between the TSVs, **TSV** represents the GSG TSVs (with pads), and **Trace** represents the 400- $\mu\text{m}$ -long GSG traces between the TSVs.

From (1) and (2)

$$\mathbf{TSV} = \sqrt{\mathbf{ChainL}^{-1} * \mathbf{Chain2L} * \mathbf{ChainL}^{-1}}. \quad (3)$$

For open–short de-embedding [32], the TSV-trace-TSV structure with the 400- $\mu\text{m}$ -long traces (thru or L structure), and open and short structures with the same distance between the TSVs were fabricated, simulated, and measured.

The open–short technique provides the losses of the traces at the base of the thru structure, which is followed by the extraction of the losses of GSG TSVs using  $ABCD$  matrices. First, the  $S$ -parameters of the open, short, and thru structures are converted to  $Y$ -parameters to evaluate the following matrices:

$$\mathbf{Matrix1}_Y = \mathbf{Thru}_Y - \mathbf{Open}_Y \quad (4)$$

and

$$\mathbf{Matrix2}_Y = \mathbf{Short}_Y - \mathbf{Open}_Y. \quad (5)$$

Next, the evaluated  $Y$ -parameter matrices are converted to  $Z$ -parameter matrices, and the  $Z$ -parameters of the traces at the base of the thru structure are obtained as follows:

$$\mathbf{Trace}_Z = \mathbf{Matrix1}_Z - \mathbf{Matrix2}_Z. \quad (6)$$

Once the  $Z$ -parameters of the trace are obtained, they are converted to  $ABCD$ -parameters to extract the TSV losses from the thru structure as follows:

$$\mathbf{TSV} = \sqrt{\mathbf{Thru} * \mathbf{Trace} * \mathbf{Trace}^{-1}}. \quad (7)$$

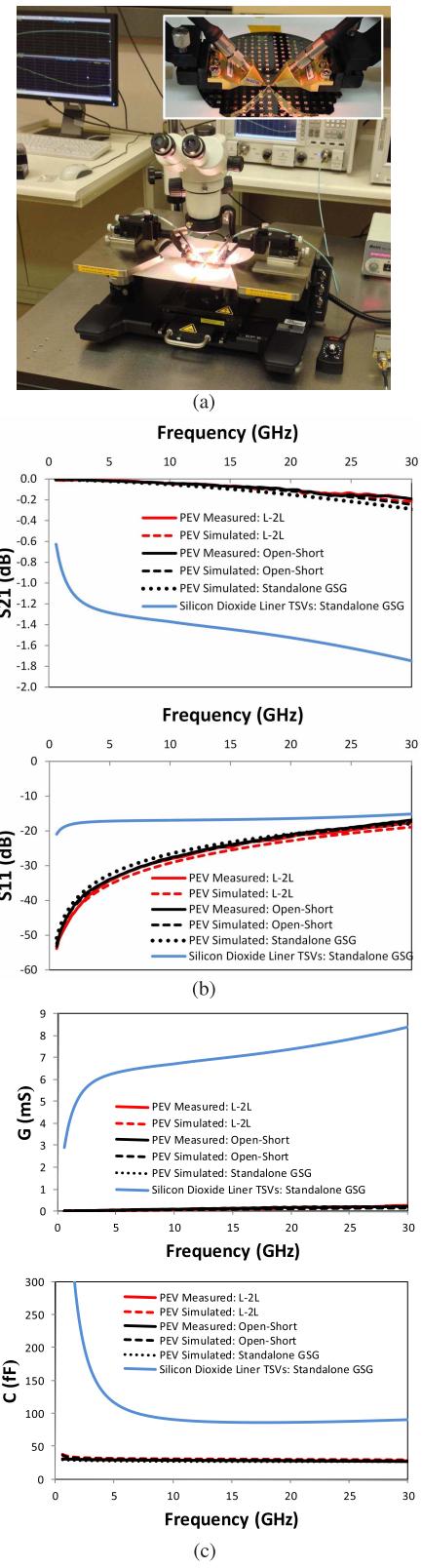

To extract the TSV losses, RF measurements were performed up to 30 GHz using a probe station with a Keysight N5245A PNA-X network analyzer and Cascade MicroTech 150- $\mu\text{m}$  pitch  $|Z|$  probes, as shown in Fig. 6(a). Prior to measurements, calibration was performed using the line-reflect-reflect-match protocol. The de-embedded TSV measurements are compared with HFSS simulations.

As shown in Fig. 6(b), the via losses attained from both de-embedding techniques are in good agreement up to 30 GHz

Fig. 6. (a) PEV RF measurement setup. (b) De-embedded results. (c) CG extractions.

with minor difference between the de-embedded and the standalone TSV loss. The de-embedding results from the measurements yield 0.22-dB insertion loss per PEV at 30 GHz. Compared with the simulated insertion loss of a standalone

Fig. 7. TSV time-domain measurement. (a) Measurement setup. (b) Time-domain measurements and extractions in ADS using RF measurements of the TSVs with  $\text{SiO}_2$  liner.

TSV with  $\text{SiO}_2$  liner, 87% reduction in insertion loss can be obtained using the PEVs at 30 GHz.

Moreover, since the key contribution to the low-loss behavior of PEVs results from the reduced capacitance and conductance compared with the TSVs with  $\text{SiO}_2$  liner (Fig. 3), capacitance and conductance of the de-embedded GSG PEVs are extracted using  $Y$ -parameters (obtained from the measured and simulated  $S$ -parameters) [25], [26]. The  $C$  and  $G$  extractions demonstrate a significant reduction in the capacitance and conductance for PEVs, as shown in Fig. 6(c).

#### D. Eye-Diagram Characterization

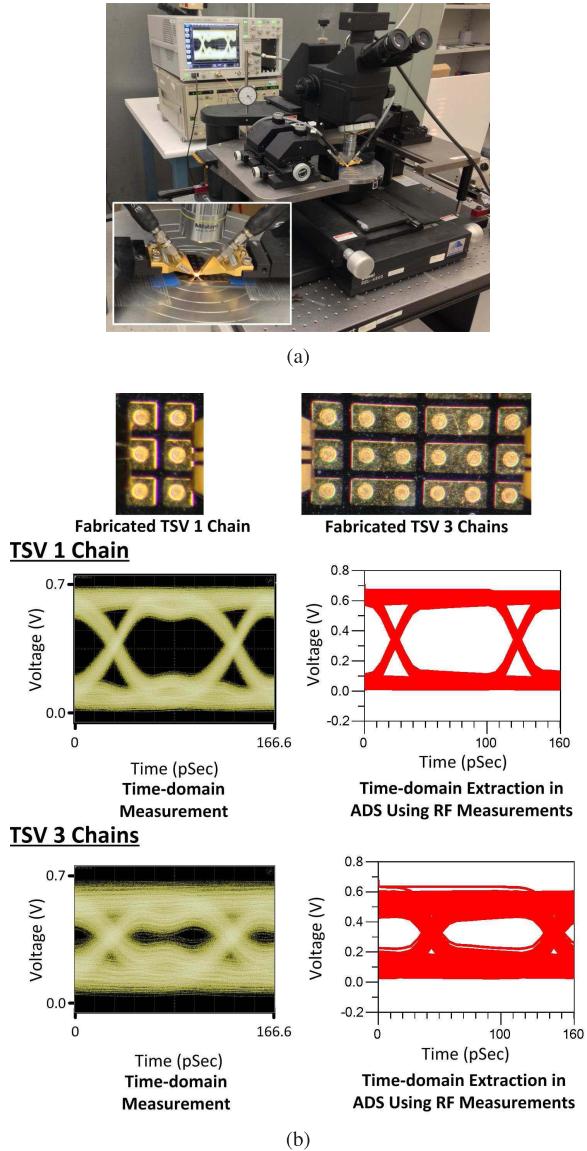

Eye diagrams assess intersymbol interference, jitter, and skew, and can thereby provide insight into TSV link performance. For TSV eye-diagram measurements, a setup, including an Anritsu MP1761C pulse pattern generator and an

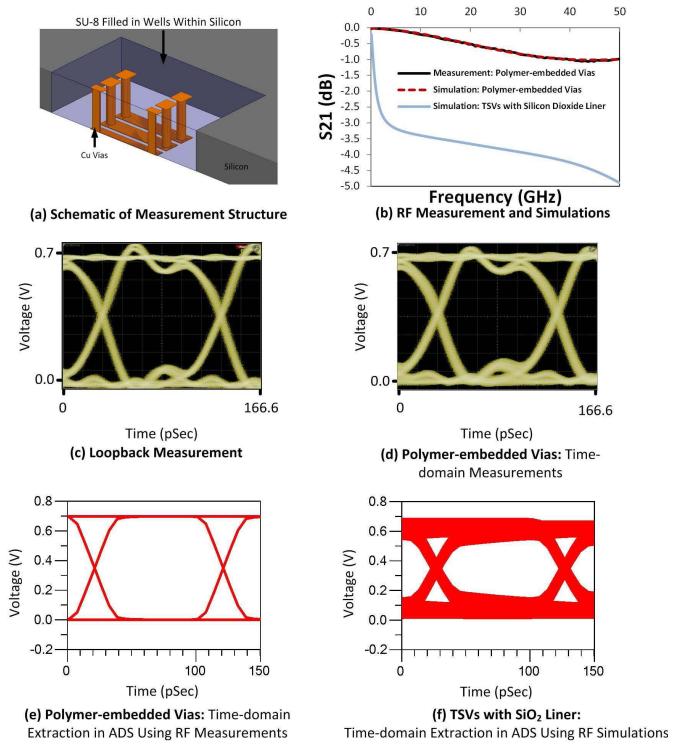

Fig. 8. Measured eye diagrams of PEVs with constructed eye diagrams in ADS using the RF measurements of PEV chains. Loop-back measurement and extracted eye diagrams from the RF simulations of the TSVs with  $\text{SiO}_2$  liner are also shown for benchmarking.

Agilent DCA-X 86100D oscilloscope, was used with Cascade MicroTech 150- $\mu\text{m}$  and 200- $\mu\text{m}$  pitch  $|Z|$  probes, as shown in Fig. 7(a). The measurements were performed with a 0.7 V (limited by the oscilloscope measurement capability) pseudo-random bit sequence (PRBS) of  $2^{11} - 1$ .

To perform the eye-diagram characterization of the fabricated PEVs, first, the measurements of chains of TSVs with  $\text{SiO}_2$  liner were performed; the TSVs are 88  $\mu\text{m}$  in diameter, 300- $\mu\text{m}$  tall, and formed on a 250- $\mu\text{m}$  pitch with the 1- $\mu\text{m}$ -thick  $\text{SiO}_2$  liner. The measured eye diagrams at 10 Gb/s for one and three chains of TSVs are shown in Fig. 7(b).

To better understand the eye-diagram measurements,  $S$ -parameter measurements of the TSV chains are performed first [using the setup in Fig. 6(a)] and imported in Keysight's Advanced Design System (ADS) to obtain eye-diagram extractions using a transient analysis. For the transient analysis, a PRBS voltage source (VtPRBS) is applied at the input (with an internal 50- $\Omega$  impedance in series corresponding to a pattern generator), and a 50- $\Omega$  termination impedance is used at the output (corresponding to an oscilloscope) of the TSV chains. With the source and termination 50- $\Omega$  impedances, the VtPRBS generates a 0.7 V peak-to-peak PRBS of  $2^{11} - 1$  with a rise-and-fall time of 30 ps [33]. The extracted eye diagrams in ADS exhibit trends and eye openings similar to the time-domain measurements. The measurements show an additional loss from cables and probes compared with the extraction yielding smaller eye openings.

Next, the eye-diagram measurements of the fabricated PEVs [the L or Thru structure in Fig. 5(a)] are explored. Before

(a)

(b)

Fig. 9. Polymer-enhanced coaxial vias. (a) Top view of the fabricated vias. (b) Extracted impedance from TSV measurements.

performing the eye-diagram measurements, loop-back measurements with a direct connection of the pattern generator to the oscilloscope were performed. Next, similar eye-diagram measurements are performed (for the fabricated PEVs) to the TSVs with  $\text{SiO}_2$  liner, as shown in Fig. 8. Moreover, using the eye-diagram extraction methodology in Keysight's ADS, eye diagrams are generated from the RF measurements of the fabricated PEVs and from the HFSS simulations of the TSVs with 1- $\mu\text{m}$ -thick  $\text{SiO}_2$  liner (10- $\Omega\cdot\text{cm}$  silicon resistivity) and the same copper via dimensions. The PEV measurements demonstrate a minimal eye closing compared with the loop-back measurements and improved eye openings and timing jitters compared with the TSVs with  $\text{SiO}_2$  liner.

### III. POLYMER-ENHANCED COAXIAL VIAS

Various coaxial TSV techniques have been shown in the literature, including laser-ablated dielectric based coaxial TSVs with annular and cylindrical signal conductors and photodefined coaxial TSVs fabricated using a temporary release layer [15], [16], [34]. This paper demonstrates coaxial vias by extending the previously described process for PEVs.

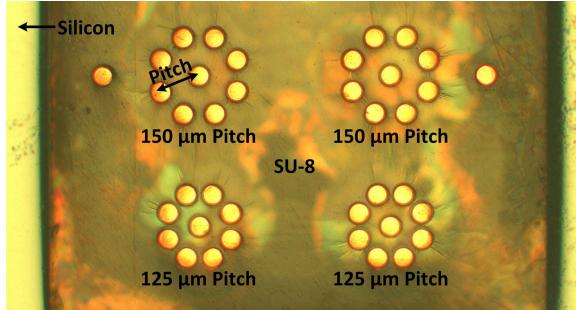

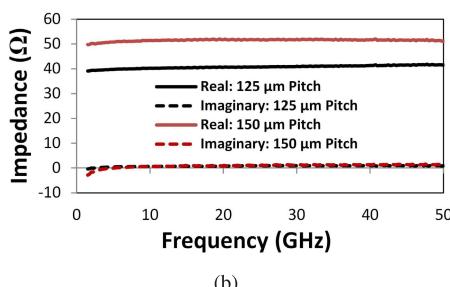

The fabrication process of coaxial vias is shown in Fig. 4. Fig. 9(a) shows the fabricated 285- $\mu\text{m}$ -tall polymer-enhanced coaxial vias within an 1800- $\mu\text{m} \times 1800\text{-}\mu\text{m}$  well in a silicon wafer (prior to the top layer metallization). The copper via diameter is 65  $\mu\text{m}$ , and the signal-to-ground via pitches are 150 and 125  $\mu\text{m}$  (i.e., two different coaxial vias).

The coaxial structure with the top metallization (Fig. 4) yields an electrically open structure for single-port measurements. Fabricating a copper layer at the base of the open structure yields an electrically short structure for single-port measurements. Using the open and short structures,

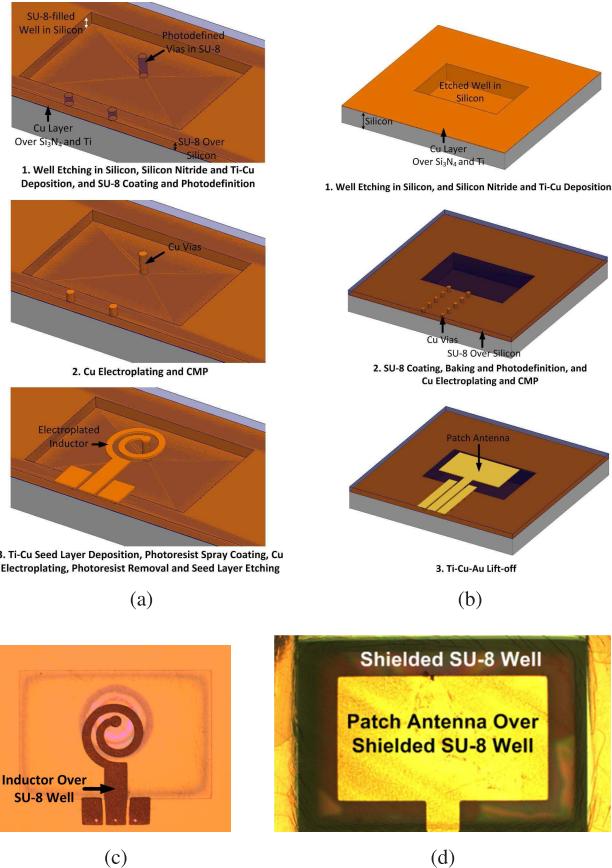

Fig. 10. Fabrication processes of (a) polymer-enhanced inductors and (b) polymer-enhanced antennas. Fabrication results of (c) inductor and (d) antenna.

high-frequency single-port measurements are performed from 1 GHz to 50 GHz. Using the measured  $S$ -parameters of the fabricated coaxial vias,  $Z$ -parameters and  $Y$ -parameters are obtained with 50  $\Omega$  as the reference impedance. Using the  $Z$ -parameters of the short structure,  $R$  and  $L$  are extracted, using the  $Y$ -parameters of the open structure,  $C$  and  $G$  are extracted [25]. Using the extracted  $RLGC$ , impedance is evaluated, as shown in Fig. 9(b), demonstrating a wideband impedance matching to approximately 50  $\Omega$  using the 150- $\mu\text{m}$  pitch vias and approximately 40  $\Omega$  using the 125- $\mu\text{m}$  pitch vias.

### IV. POLYMER-ENHANCED INDUCTOR AND ANTENNA

With respect to the RF inductors, various techniques have been demonstrated in the literature, including off-chip inductors that are: 1) formed over dielectric-coated trenches in silicon [18]; 2) over glass interposers [9]; 3) using vias in the glass interposers [9]; 4) under a molding compound [4]; and 5) over polymer wells [35]. The inductor in this paper is implemented utilizing the photodefined polymer-enhanced silicon interposer technology demonstrated earlier yielding a high  $Q$ -factor using a one-port measurement structure. The proposed inductor can be fabricated in parallel to PEVs, easing the fabrication of the envisioned silicon interposer system, as shown in Fig. 1. The inductors are fabricated over shallow

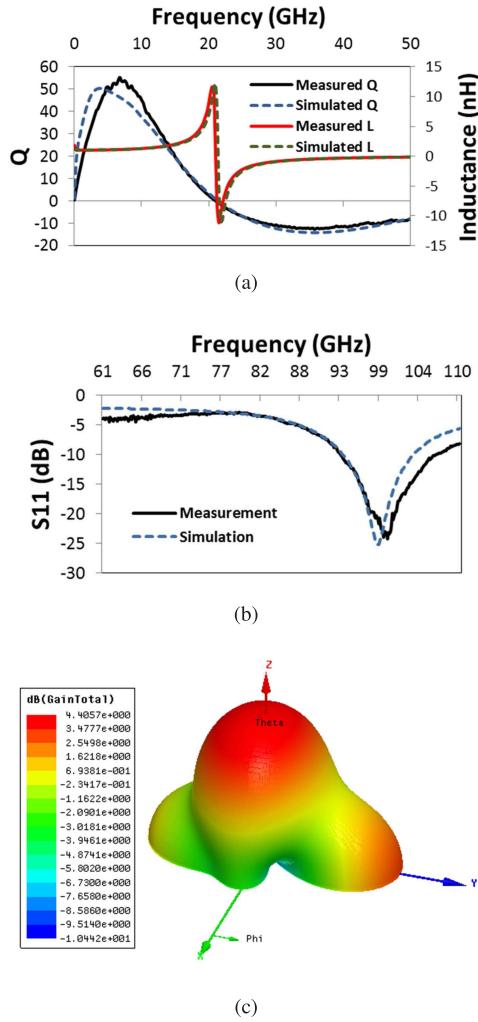

Fig. 11. Measurement results of (a) inductor, (b) antenna, and (c) antenna gain simulation.

wells (100- $\mu$ m deep) in a silicon wafer to ease fabrication, and since an appreciable improvement is not observed in the  $Q$ -factor beyond 100- $\mu$ m well depth. Spiral inductors have been implemented with the photodefined copper vias in the polymer wells to show the benefits of the photodefined polymer-enhanced silicon interposer technology using a simpler inductor geometry.

With respect to the antennas, various techniques have been demonstrated in the literature, including antennas over: 1) high-resistivity silicon with cavity backing [5]; 2) molding material [36]; 3) suspended SU-8 substrate [37]; and 4) polymer-filled wells [38]. Similar to the inductor, utilizing the photodefined polymer-enhanced silicon interposer technology, a high radiation-efficiency antenna is demonstrated in this paper. Various microfabricated antenna types, such as patch, folded dipole, slot, and Yagi-Uda, have been explored in [5] and [38]–[40]. Patch antennas have been selected in this paper owing to their ease of fabrication and good radiation control [41]. The rectangular patch has been selected instead of circular, elliptical, triangular, or annular shapes in order to achieve higher gain and bandwidth [41].

### A. Fabrication

As shown in Fig. 10, the fabrication processes of the inductor and antenna begin with the etching of wells in a silicon wafer followed by silicon nitride and titanium-copper deposition. Next, SU-8 filling, photodefinition, copper electroplating, and CMP are performed followed by the fabrication of the inductors and antennas. The inductors are fabricated using electroplating, and antennas are fabricated using lift-off.

Fig. 10(c) shows the fabricated 8–12- $\mu$ m-thick 1.5 turn inductor with the 55–65- $\mu$ m-wide traces on a 100- $\mu$ m pitch, and over a 1530  $\mu$ m  $\times$  1030  $\mu$ m and 100- $\mu$ m deep well. Moreover, Fig. 10(d) shows the fabricated 1100  $\mu$ m  $\times$  650  $\mu$ m and 2- $\mu$ m-thick patch antenna over a 1530  $\mu$ m  $\times$  1030  $\mu$ m and 280- $\mu$ m deep well.

### B. Characterization

For the fabricated inductor, high-frequency measurements were performed up to 50 GHz, and inductance and  $Q$ -factor were extracted demonstrating a peak  $Q$ -factor of 55 at 6.75 GHz ( $f_{Q_{\text{peak}}}$ ) and a 1.14-nH inductance at  $f_{Q_{\text{peak}}}$  with a self-resonance frequency at 21 GHz, as shown in Fig. 11(a).

Moreover, for the fabricated antenna, high-frequency measurements were performed from 60 GHz to 110 GHz demonstrating a 13.35-GHz 10-dB return loss bandwidth at the center frequency of 100 GHz, as shown in Fig. 11(b). In addition, an HFSS simulation of the fabricated antenna shows a gain of 4.4 dBi and 70% radiation efficiency at 100 GHz. A radiation pattern simulation result is shown in Fig. 11(c) demonstrating a high-gain primary lobe. A further improvement in the gain, radiation efficiency, and radiation pattern could be obtained by improving the antenna and feed designs, and using a polymer material with a lower loss tangent (benzocyclobutene, for example) in the future.

## V. CONCLUSION

This paper demonstrates the fabrication and characterization of photodefined PEVs, coaxial TSVs, inductors, and antennas for mixed-signal heterogeneous integration using silicon interposers. RF analysis, fabrication, de-embedding up to 30 GHz, and eye-diagram measurements are demonstrated for PEVs, showing their enhanced electrical performance compared with the TSVs with  $\text{SiO}_2$  liner. Moreover, fabrication and impedance extraction are demonstrated for coaxial TSVs showing wideband impedance matching. Finally, the fabrication and characterization of polymer-enhanced inductor and antenna are demonstrated proving their enhanced electrical performance.

## ACKNOWLEDGMENT

The authors would like to thank the IBM Ph.D. fellowship for the academic year 2014–2015. They would also like to thank S. Hu and Dr. H. Wang for their help with time-domain measurements and Dr. C. Ulusoy, Dr. W. Khan, P. Song, Dr. J. Cressler, and Dr. J. Papapolymerou for their help with antenna measurements.

## REFERENCES

- [1] C. Erdmann *et al.*, "A heterogeneous 3D-IC consisting of two 28 nm FPGA die and 32 reconfigurable high-performance data converters," *IEEE J. Solid-State Circuits*, vol. 50, no. 1, pp. 258–269, Jan. 2015.

- [2] W. S. Liao *et al.*, "A high-performance low-cost chip-on-wafer package with sub- $\mu$ m pitch Cu RDL," in *IEEE Symp. VLSI Technol., Dig. Tech. Papers*, Jun. 2014, pp. 1–2.

- [3] M. S. Bakir and J. D. Meindl, *Integrated Interconnect Technologies for 3D Nanoelectronic Systems*. Norwood, MA, USA: Artech House, 2009.

- [4] C. C. Liu *et al.*, "High-performance integrated fan-out wafer level packaging (InFO-WLP): Technology and system integration," in *Proc. IEEE Int. Electron Devices Meeting (IEDM)*, Dec. 2012, pp. 14.1.1–14.1.4.

- [5] L. Dussopt *et al.*, "Silicon interposer with integrated antenna array for millimeter-wave short-range communications," in *IEEE MTT-S Int. Microw. Symp. Dig.*, Jun. 2012, pp. 1–3.

- [6] W. Roh *et al.*, "Millimeter-wave beamforming as an enabling technology for 5G cellular communications: Theoretical feasibility and prototype results," *IEEE Commun. Mag.*, vol. 52, no. 2, pp. 106–113, Feb. 2014.

- [7] M. Porranzl, C. Wagner, H. Jaeger, and A. Stelzer, "An active quasi-circulator for 77 GHz automotive FMCW radar systems in SiGe technology," *IEEE Microw. Wireless Compon. Lett.*, vol. 25, no. 5, pp. 313–315, May 2015.

- [8] W. T. Khan, A. C. Ulusoy, and J. Papapolymerou, "D-band characterization of co-planar wave guide and microstrip transmission lines on liquid crystal polymer," in *Proc. 63rd IEEE Electron. Compon. Technol. Conf. (ECTC)*, May 2013, pp. 2304–2309.

- [9] W. C. Lai *et al.*, "300 mm size ultra-thin glass interposer technology and high-Q embedded helical inductor (EHI) for mobile application," in *Proc. IEEE Int. Electron Devices Meeting (IEDM)*, Dec. 2013, pp. 13.4.1–13.4.4.

- [10] M. Detalle *et al.*, "Minimizing interposer warpage by process control and design optimization," in *Proc. IEEE 64th Electron. Compon. Technol. Conf. (ECTC)*, May 2014, pp. 33–40.

- [11] M. Sunohara, H. Sakaguchi, A. Takano, R. Arai, K. Murayama, and M. Higashi, "Studies on electrical performance and thermal stress of a silicon interposer with TSVs," in *Proc. IEEE 60th Electron. Compon. Technol. Conf. (ECTC)*, Jun. 2010, pp. 1088–1093.

- [12] J. S. Pak, C. Ryu, and J. Kim, "Electrical characterization of trough silicon via (TSV) depending on structural and material parameters based on 3D full wave simulation," in *Proc. Int. Conf. Electron. Mater. Packag. (EMAP)*, Nov. 2007, pp. 1–6.

- [13] P. A. Thadesar and M. S. Bakir, "Novel photo-defined polymer-enhanced through-silicon vias for silicon interposers," *IEEE Trans. Compon., Packag., Manuf. Technol.*, vol. 3, no. 7, pp. 1130–1137, Jul. 2013.

- [14] Q. Chen, C. Huang, D. Wu, Z. Tan, and Z. Wang, "Ultralow-capacitance through-silicon vias with annular air-gap insulation layers," *IEEE Trans. Electron Devices*, vol. 60, no. 4, pp. 1421–1426, Apr. 2013.

- [15] D. H. Jung *et al.*, "30 Gbps high-speed characterization and channel performance of coaxial through silicon via," *IEEE Microw. Wireless Compon. Lett.*, vol. 24, no. 11, pp. 814–816, Nov. 2014.

- [16] S. W. Ho, S. W. Yoon, Q. Zhou, K. Pasad, V. Kripesh, and J. H. Lau, "High RF performance TSV silicon carrier for high frequency application," in *Proc. 58th IEEE Electron. Compon. Technol. Conf. (ECTC)*, May 2008, pp. 1946–1952.

- [17] H. M. Cheema and A. Shamim, "The last barrier: On-chip antennas," *IEEE Microw. Mag.*, vol. 14, no. 1, pp. 79–91, Jan./Feb. 2013.

- [18] M. Rais-Zadeh, J. Laskar, and F. Ayazi, "High performance inductors on CMOS-grade trenched silicon substrate," *IEEE Trans. Compon. Packag. Technol.*, vol. 31, no. 1, pp. 126–134, Mar. 2008.

- [19] I. Ndip *et al.*, "High-frequency modeling of TSVs for 3-D chip integration and silicon interposers considering skin-effect, dielectric quasi-TEM and slow-wave modes," *IEEE Trans. Compon., Packag., Manuf. Technol.*, vol. 1, no. 10, pp. 1627–1641, Oct. 2011.

- [20] V. Sukumaran *et al.*, "Design, fabrication, and characterization of ultrathin 3-D glass interposers with through-package-vias at same pitch as TSVs in silicon," *IEEE Compon., Packag., Manuf. Technol.*, vol. 4, no. 5, pp. 786–795, May 2014.

- [21] T. G. Lim *et al.*, "Through silicon via interposer for millimetre wave applications," in *Proc. IEEE 61st Electron. Compon. Technol. Conf. (ECTC)*, May/Jun. 2011, pp. 577–582.

- [22] J.-Y. Lee, S.-W. Lee, S.-K. Lee, and J.-H. Park, "Through-glass copper via using the glass reflow and seedless electroplating processes for wafer-level RF MEMS packaging," *J. Micromech. Microeng.*, vol. 23, no. 8, p. 085012, Aug. 2013.

- [23] A. del Campo and C. Greiner, "SU-8: A photoresist for high-aspect-ratio and 3D submicron lithography," *J. Micromech. Microeng.*, vol. 17, pp. R81–R95, May 2007.

- [24] J. Kim *et al.*, "High-frequency scalable electrical model and analysis of a through silicon via (TSV)," *IEEE Trans. Compon., Packag., Manuf. Technol.*, vol. 1, no. 2, pp. 181–195, Feb. 2011.

- [25] Z. Xu and J.-Q. Lu, "Through-silicon-via fabrication technologies, passives extraction, and electrical modeling for 3-D integration/packaging," *IEEE Trans. Semicond. Manuf.*, vol. 26, no. 1, pp. 23–34, Feb. 2013.

- [26] I. Ndip *et al.*, "Analytical, numerical-, and measurement-based methods for extracting the electrical parameters of through silicon vias (TSVs)," *IEEE Trans. Compon., Packag., Manuf. Technol.*, vol. 4, no. 3, pp. 504–515, Mar. 2014.

- [27] J. Robertson, "High dielectric constant oxides," *Eur. Phys. J. Appl. Phys.*, vol. 28, pp. 265–291, Dec. 2004.

- [28] A. Ghannam, V. Viallon, D. Bourrier, and T. Parra, "Dielectric microwave characterization of the SU-8 thick resin used in an above IC process," in *Proc. Eur. Microw. Conf. (EuMC)*, Sep./Oct. 2009, pp. 1041–1044.

- [29] F. D. Mbairi and H. Hesselbom, "High frequency design and characterization of SU-8 based conductor backed coplanar waveguide transmission lines," in *Proc. Int. Symp. Adv. Packag. Mater., Process., Properties Interfaces*, Mar. 2005, pp. 243–248.

- [30] R. G. Pierce, R. Islam, R. M. Henderson, and A. Blanchard, "SU-8 2000 millimeter wave material characterization," *IEEE Microw. Wireless Compon. Lett.*, vol. 24, no. 6, pp. 427–429, Jun. 2014.

- [31] H.-T. Yen *et al.*, "TSV RF de-embedding method and modeling for 3DIC," in *Proc. 23rd Annu. SEMI Adv. Semiconductor Manuf. Conf. (ASMC)*, May 2012, pp. 394–397.

- [32] Y.-C. Chang, D.-C. Chang, S. S. H. Hsu, J.-H. Lee, S.-G. Lin, and Y.-Z. Juang, "A matrix-computation based methodology for extracting the S-parameters of interconnects in advanced packaging technologies," in *Proc. IEEE Asia-Pacific Microw. Conf. (APMC)*, Dec. 2011, pp. 1909–1912.

- [33] H. Kim *et al.*, "Measurement and analysis of a high-speed TSV channel," *IEEE Trans. Compon., Packag., Manuf. Technol.*, vol. 2, no. 10, pp. 1672–1685, Oct. 2012.

- [34] J.-M. Yook, D. Kim, J.-C. Park, C.-Y. Kim, S. H. Yi, and J. C. Kim, "Low-loss and high-isolation through silicon via technology for high performance RF applications," in *Proc. 44th Eur. Microw. Conf. (EuMC)*, Oct. 2014, pp. 996–999.

- [35] Y. M. Khoo, T. G. Lim, S. W. Ho, R. Li, Y.-Z. Xiong, and X. Zhang, "Enhancement of silicon-based inductor Q-factor using polymer cavity," *IEEE Trans. Compon., Packag., Manuf. Technol.*, vol. 2, no. 12, pp. 1973–1979, Dec. 2012.

- [36] C.-H. Tsai *et al.*, "Array antenna integrated fan-out wafer level packaging (InFO-WLP) for millimeter wave system applications," in *Proc. IEEE Int. Electron Devices Meeting (IEDM)*, Dec. 2013, pp. 25.1.1–25.1.4.

- [37] H. Mopidevi *et al.*, "Three-dimensional microfabricated broadband patch antenna for WiGig applications," *IEEE Antennas Wireless Propag. Lett.*, vol. 13, pp. 828–831, 2014.

- [38] S. Hu, Y.-Z. Xiong, L. Wang, R. Li, and T. G. Lim, "A millimeter-wave wideband high-gain antenna and its 3D system-in-package solution in a TSV-compatible technology," in *Proc. IEEE 61st Electron. Compon. Technol. Conf. (ECTC)*, May 2011, pp. 869–872.

- [39] J. Hacker *et al.*, "A 16-element transmit/receive Q-band electronically steerable subarray tile," in *Proc. IEEE MTT-S Int. Microw. Symp.*, Jun. 2012, pp. 1–3.

- [40] W. T. Khan, A. L. V. Lopez, A. C. Ulusoy, and J. Papapolymerou, "Packaging a W-band integrated module with an optimized flip-chip interconnect on an organic substrate," *IEEE Trans. Microw. Theory Techn.*, vol. 62, no. 1, pp. 64–72, Jan. 2014.

- [41] R. Waterhouse, *Microstrip Patch Antennas: A Designer's Guide*. Boston, MA, USA: Springer, Feb. 2003.

**Paragkumar A. Thadesar** (S'09–M'15) received the B.E. degree with a gold medal in electronics and communication engineering from VVP Engineering College, Rajkot, India, and the M.S. and Ph.D. degrees in electrical and computer engineering from the Georgia Institute of Technology, Atlanta, GA, USA, in 2011 and 2015, respectively.

His Ph.D. degree was focused on electrical design, fabrication, and high-frequency characterization of through-silicon vias and RF platforms.

Dr. Thadesar received the IBM Ph.D. Fellowship Award from 2014 to 2015, the Outstanding Interactive Presentation Paper Award at the IEEE Electronic Components and Technology Conference in 2013, a Best-in-Session Award at the Semiconductor Research Corporation TECHCON Conference in 2013, a third place Microelectronics Foundation Prize at the International Microelectronics Assembly and Packaging Society Device Packaging in 2013, and the best student paper awards at the Global Interposer Technology Workshop in 2011 and 2012.

**Muhammed S. Bakir** (SM'12) received the B.E.E. degree from Auburn University, Auburn, AL, USA, in 1999, and the M.S. and Ph.D. degrees in electrical and computer engineering from the Georgia Institute of Technology (Georgia Tech), Atlanta, GA, USA, in 2000 and 2003, respectively.

He is currently an Associate Professor with the School of Electrical and Computer Engineering, Georgia Tech. His current research interests include 3-D electronic system integration, advanced cooling and power delivery for 3-D systems, biosensors and their integration with CMOS circuitry, and nanofabrication technology.

Dr. Bakir was a recipient of the 2013 Intel Early Career Faculty Honor Award, the 2012 DARPA Young Faculty Award, and the 2011 IEEE Components, Packaging, and Manufacturing Technology (CPMT) Society Outstanding Young Engineer Award. He and his research group have received more than 15 conference and student paper awards, including five from the IEEE Electronic Components and Technology Conference, four from the IEEE International Interconnect Technology Conference, and one from the IEEE Custom Integrated Circuits Conference. His group received the 2014 Best Paper of the IEEE TRANSACTIONS ON COMPONENTS, PACKAGING, AND MANUFACTURING TECHNOLOGY in the area of advanced packaging. He was an Invited Participant in the 2012 National Academy of Engineering Frontiers of Engineering Symposium. In 2015, he was elected by the IEEE CPMT Society to serve as a Distinguished Lecturer, and was an Invited Speaker at the U.S. National Academies Frontiers of Sensor Science Symposium. He is an Editor of the IEEE TRANSACTIONS ON ELECTRON DEVICES and an Associate Editor of the IEEE TRANSACTIONS ON COMPONENTS, PACKAGING, AND MANUFACTURING TECHNOLOGY.